|

|

|

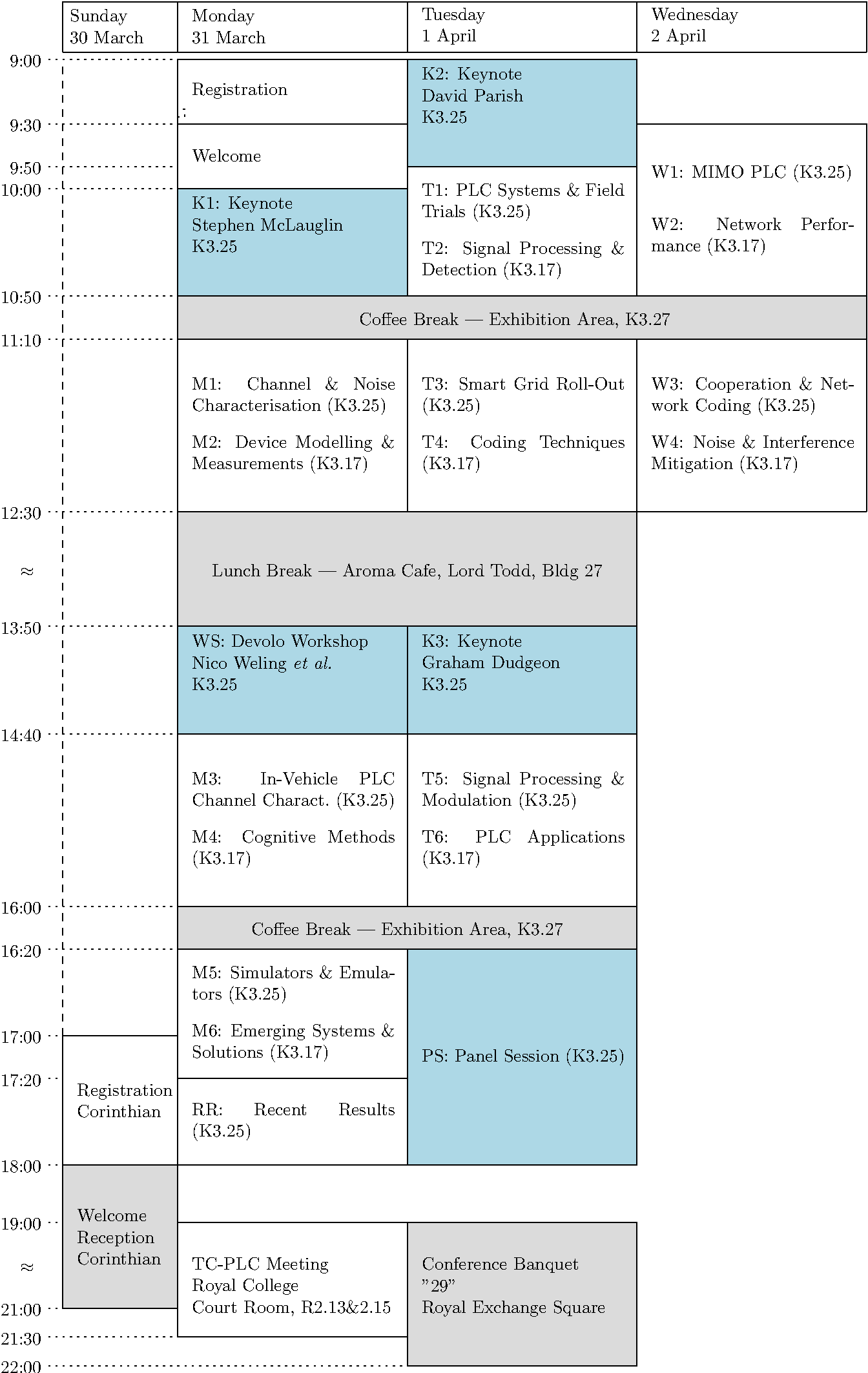

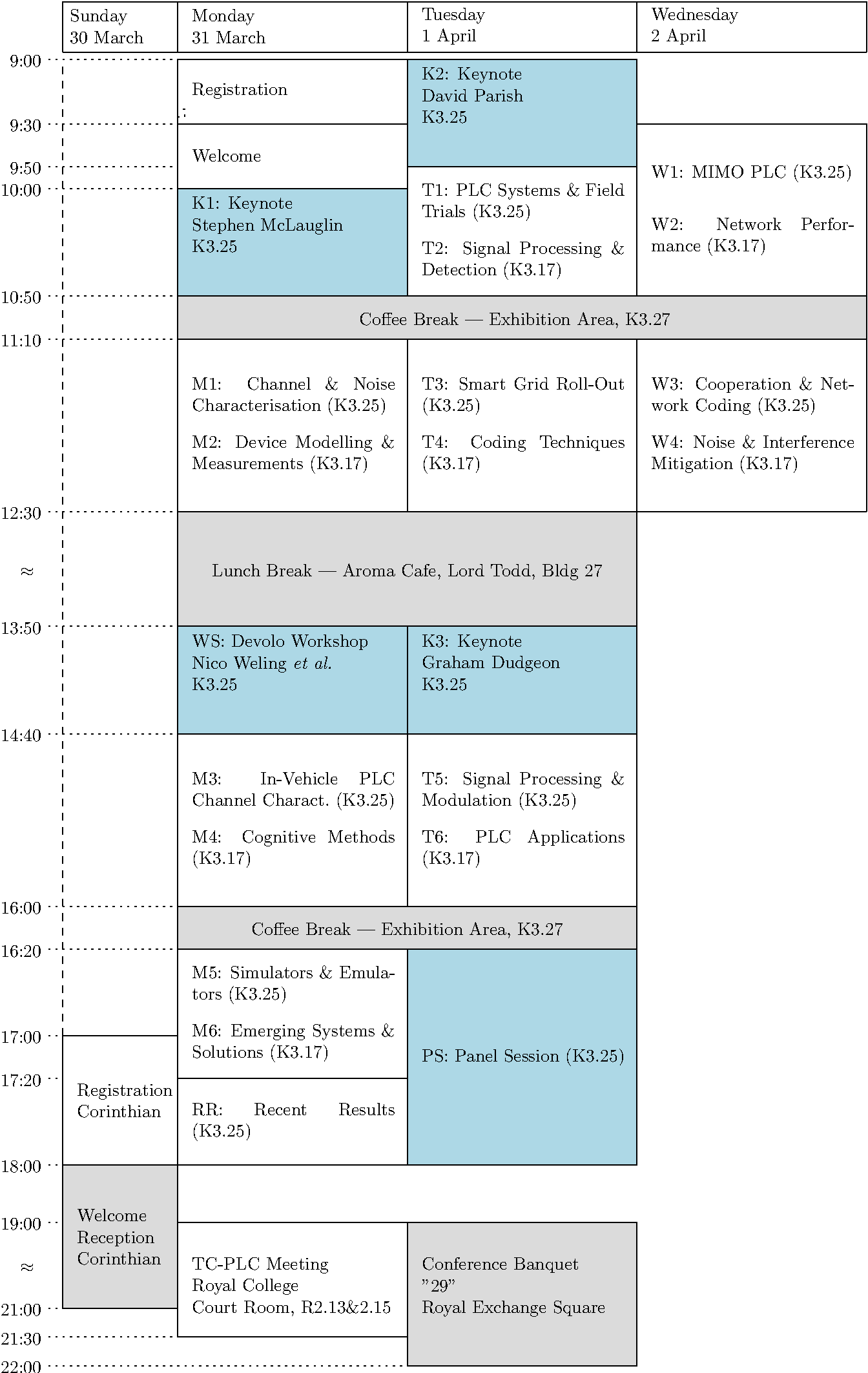

Keynote 1: The Statistics of Impulse Noise in xDSL Systems |

Stephen McLaughlin (Heriot-Watt University, Edinburgh)

Monday 10:00-10:50, K3.25

Abstract. This talk will discuss impulse noise in xDSL systems ad how they are very similar to those in power line communication systems. The talk will discuss the sources of impulse noise, discuss the analysis adopted of real world data and illustrate a method for simulating impulses with appropriate amplitude, spectral, and inter-arrival characteristics. The statistics used to develop the parameters of this model are based on statistics derived from observations of impulse noise on the telephone networks of British Telecom (BT) and Deutsche Telekom (DT).

Stephen McLaughlin is Head of School of Engineering and Physical Sciences at Heriot-Watt University in Edinburgh. He studied at the University of Glasgow, and, after being a Development Engineer at Barr and Stroud and MEL Ltd, at the University of Edinburgh. He has held a number of academic positions within the University of Edinburgh including that of Director of Research and Deputy Head of the School of Engineering. His research interests lie in the

fields of adaptive signal processing and non-linear dynamical systems theory and their applications to biomedical, geophysical, imaging and communication systems. Steve is a Fellow of both the Royal Academy of Engineering and the Royal Society of Edinburgh, and a Fellow of the IEEE. |

|

Keynote 2: Anomaly Detection in Communication Network Traffic |

David Parish (Loughborough University, Loughborough, UK)

Tuesday 9:00-9:50, K3.25

Abstract. This presentation will consider the role of anomaly detection in the understanding of communication network traffic. An anomaly in this case is a statistical variation from the norm in some aspect of the traffic or a derivative of it. Traffic characteristics will be briefly discussed, as will a summary of some of the approaches used to detect anomalies in these. Application areas for anomaly detection including incident and intrusion detection will be considered and some specific examples and systems from the presenter’s research will be described. These will include the usage of anomalies in frame delay to identify incidents in frame or packet switched networks; the identification of attacks in the core of an ISP network and the identification of frame injections into a wireless network.

David Parish is Professor of Communication Networks and Dean in the School of Electronic, Electrical and Systems Engineering at Loughborough University. He leads the High Speed Networks Group which conducts research into network measurement and abuse detection and has lead projects which have installed purpose designed measurement and cyber attack detection equipment into three operational networks run by commercial (BT and NTL/VirginMedia) or service organisations (JANET UK). His current research interests include the use of cross layer techniques for internet attack detection and performance monitoring approaches for cloud networks. He has published over 180 research papers and has lead over £2.5M of research project funding. He is a member of the EPSRC College of Peers and has been a member of the ICT SAT. He is currently Treasurer and Deputy Chair of UKRI IEEE COMSOC Chapter. |

|

Keynote 3: Addressing the Challenges in Delivering the Smart Grid through Model-Based Design |

Graham Dudgeon (Mathworks Ltd, USA)

Tuesday 13:50-14:40, K3.25

Abstract. The emergence of smart technologies has provided a technological framework that holds great promise for positively impacting the security, efficiency, reliability and economy of electric system operation. Realizing the maximum operational potential of an integrated system requires strong collaboration among multiple engineering disciplines. For micro-grids and other smart grid technologies communication system engineers, electrical power engineers, control system engineers, must work together in the design process to mitigate the risks associated with physical integration and operation.

This presentation will consider micro-grid as the main proxy for smart grid, and we will share observations on how Model-Based Design provides a framework that allows collaboration among engineering disciplines, reduces the risk associated with engineering design, and enables engineers to realize the ‘smart’ of smart grid.

Graham Dudgeon is the Energy Industry Manager at MathWorks, and works closely with the Electric Power and Oil & Gas industries worldwide. Before his role as industry manager, Graham was a Principal Technical Consultant at MathWorks and worked with a broad range of customers in the Electric Machinery, Aerospace, Defence, Automative, Transport and Medical industries. Graham’s technical experience and expertise includes; electric grid simulation (transmission and distribution), renewable energy simulation (wind farm and solar farm operation and grid integration), control system design and analysis, data analytics, and power electronics.

Before joining MathWorks, Graham worked at the Defence Evaluation and Research Agency (DERA), an agency of the UK Ministry of Defence, in the Flight Management and Control Department, and also as a Senior Research Fellow at the Rolls-Royce University Technology Centre in Electrical Power Systems at the University of Strathclyde.

|

|

Devolo Workshop on Testing MIMO-PLC Devices on a Broadband Powerline Channel Emulator

Nico Weling, Andreas Engelen and Stefan Thiel (Devolo AG, Aachen, Germany)

Tuesday 13:50-14:40, K3.25

Abstract.

One of the key challenges faced by silicon vendors, product manufacturers and service providers today is the testing of PLC devices under real world conditions. Although PLC devices are now deployed in the field for several years the testing of PLC modems becomes more and more difficult. This results from several technical improvements.

Until today, most of deployed PLC devices are SISO modems and the PLC network can be seen as a single channel differential network between the live and the neutral wire. Testing these type of device could be done by decoupling the RF signals from the powerline using a coupler and then adjusting the attenuation between both modems with a digital step attenuator. Recent PLC devices supporting the HomePlug AV2 standard are much more complex and thus require much more complex testing capabilities. AV2 based PLC devices are using a primary and secondary transmit path. Depending on the type of coupling various combinations of the three wires in a powerline network are possible to transmit the data through these two paths.

In the workshop we will present a solution using a very flexible FPGA based powerline channel emulator for broadband MIMO PLC devices. The first part of the workshop will show from where we get all the data to feed the channel emulator. Various sources can be used to collect channel information which are needed to load into the emulator.

In the second part we will show the electrical properties of the emulator such as the huge dynamic range, line synchronization capabilities, frequency ranges or the number of channels.

In the last part of the workshop we will go through a set of test cases to demonstrate the wide range of testing capabilities. A test case for loading real world channel characteristic including a MIMO channel transfer function and cylostationary noise scenarios. A test case demonstrating how to test the adaptive power management requirement from the recently published EN 50561-1 standard. A test case for demonstrating the cognitive frequency exclusion feature also required by EN 50561-1.

Dipl.-Ing. Nico Weling is working as Director of Research for devolo AG, Aachen/Germany. He joined devolo in April 2004 as hardware engineer and took over the leadership of the hardware-development group in 2007. He received his degree in electrical engineering (Dipl.-Ing.) from the University of Applied Sciences in Aachen/Germany in January 2000. In the year 2000 he worked for PHILIPS Research Laboratories Aachen GmbH in the area of FPGA design. From 2001 till 2004 worked at ERICSSON Eurolab GmbH – Research & Development of GSM, GPRS and UMTS mobile networks.

Dipl.-Ing. Andreas Engelen is working as FPGA and Hardware Designer at the Research Department for devolo AG, Aachen/Germany. He joined devolo in October 2012 as Research Engineer. He received his degree in electrical engineering (Dipl.-Ing.) from the University of Applied Sciences in Aachen/Germany in April 2001. During the years 2001-2012 he worked for GEMIT GmbH in the area of FPGA and DSP designs.

Dipl.-Ing. Stephan Thiel is working as Research Engineer for devolo AG, Aachen/Germany. He joined devolo in 2008 as design verification and test engineer and change into the research department in 2010. He received his degree in electrical engineering (Dipl.-Ing.) from the University of Applied Sciences in Aachen/Germany in 2008.

|

|

Panel: What Research Do We Need for PLC 2020?

Chair: Lutz Lampe (University of British Columbia, Canada)

Tuesday 16:20-18:00, K3.25

Panellists: Gerd Bumiller (Hochschule Ruhr West, Germany), Il Han Kim (Texas Instruments, USA), Michael Koch (Devolo, Germany), David Rieken (Aclara, USA), Alberto Sendin Escalona (Iberdrola, Spain), Andrea Tonello (University of Udine & WiTiKee, Italy)

|

|

The following presentations reflect on recent

technical developments, which are for discussion only

and not published as part of ISPLC 2014:

- On Efficiency and Validity of Previous Homeplug MAC Performance Analysis

David Malone and Cristina Cano (Hamilton Institute,

NUI Maynooth, Ireland):

The Medium

Access Control protocol of Power Line

Communication networks (defined in Homeplug

and IEEE 1901 standards) has received

relatively modest attention from the

research community. As a consequence, there

is only one analytic model that complies

with the standardised MAC procedures. We

identify two important limitations of the

existing analytic model: high computational

expense and predicted results just prior to

the predicted saturation point do not

correspond to long-term network

performance. We will present a

simplification of the previously defined

analytic model of Homeplug MAC able to

substantially reduce its complexity and

demonstrate that the previous performance

results just before predicted saturation

correspond to a transitory phase.

- Improving the Performance of Narrowband Powerline Communication Systems by Exploiting the Space Dimension

Kamel Shibli and Mike Heidrich (Fraunhofer Institut ESK, Munich, Germany):

Different standards are available today to push the development of powerline communication (PLC) in smart grids. In this presentation, we focus on the IEEE 1901.2 standard in the low voltage network and study the performance of the system using multiple ports for data communication. This is also known as Multiple Input Multiple Output (MIMO). In addition, we present a multi-conductor transmission line channel model for four-conductor sector shaped cables, which takes the coupling between the wires into account. A short comparison of the capacity gain with respect to the single-wire case is also given.

- Realistic Hardware Channel Emulation (HACE) for PLC System Testing

Andrea Tonello (WiTiKee s.r.l., Italy):

Realistic emulation of PLC channels is of great importance for

modem design and testing. We will present recent results about broadband

channel measurements and discuss a novel approach to emulate statistically

representative channels. Existing emulators target the channel frequency

response, i.e., the attenuation exhibited by the channel from the

transmission to the receiver port. However, the line impedance, i.e., the

load seen by the transmitter, is even more important for what concerns the

design of the analog front end and the capability of the latter to drive

correctly the line. Despite the challenge of emulating broadband channels in

terms of their line impedance and response due to their severe frequency

variability, we show that this is possible with a novel hardware platform

named HACE. HACE has been designed and realized with an efficient synthesis

approach. The platform allows the test of both the modem analog front-end

and the analysis of the modem-to-modem performance. It ensures unbiased

results that may not be guaranteed by soft-implemented emulation.

Please e-mail Stephan Weiss (stephan.weissif you are interested to present in this session.

|

|

|